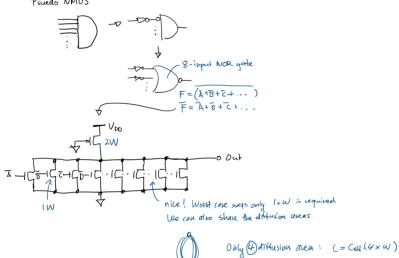

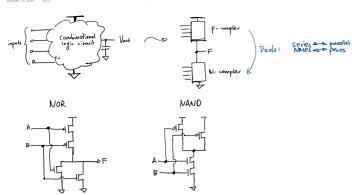

## Static CMOS Combinational Logic

Gleveral steps for logic f(A,B,C....)

- (1) Simplify function  $\overline{f}(A,B,...)$ function could be + or  $\times$

- Design MMOS (pull down)

† is pulled<br/>

X is sectors

- 3 Derign PMOS (pau q) just make dualstswitch series en pambel

- 3 Part P complex & N complex on top of each other

- (5) Connect Input & Output

- 6 Size the Mos'es

Gate Sizing depends on worst-case scenario (to match with the default inverter)

Default Involver:

For parallel only one is one

(max. resistance)

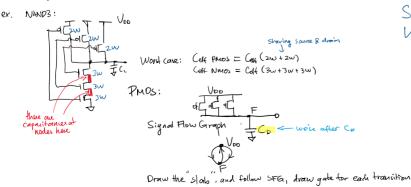

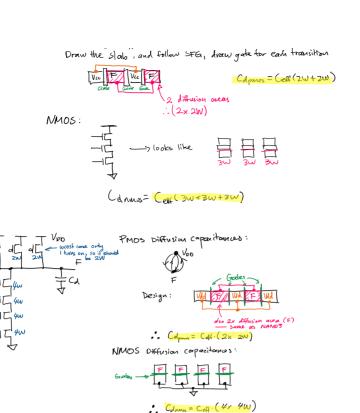

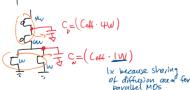

## Diffusion (apacitances:

Self capacitaines mostly dominated by drain/fulk cap. Load capacitures mostly dominated by gate cap

Vice For Caparos = Cell (2W+2W)

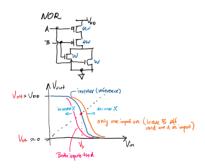

VTC & Noise Margin

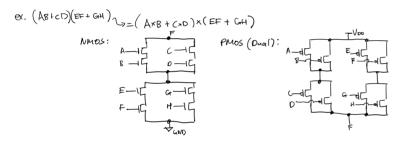

ex. NAND4

→ consider two extreme cases L> All input on L> only one imput on

- All characteristics are bracketed between

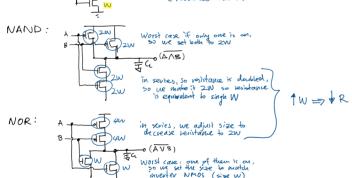

NAND:

We size the MOS to match Resistance,

But what about capacitance? 4 Because load capacitances should be much larger, I so the entra capacitances shouldn't matter too much.

Total capacitacues:

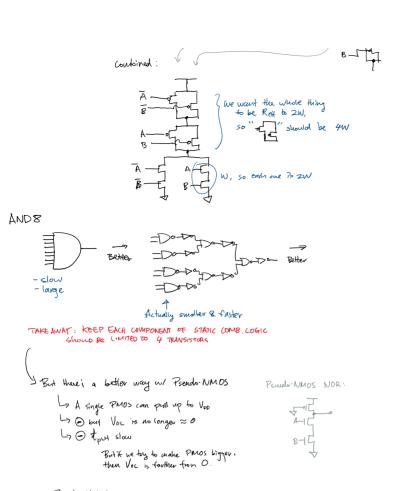

XOR Gate. Ex.

Function of XOR:

$$f(A,B) = (\overline{A}B + AB)$$

$f(A,B) = \overline{A}B + AB$

A B Out

Pull Down: Pull up( Dank)

A TATE

B B THE

Couloired:

Only one input test:

B is off: — equivalent circuit:

All input on test:

Both A&B fied equivalent circuit: