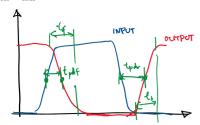

RISE TIME - (tr. till) time taken from 10% to 90% FALL TIME ~ (tr. the) time taken from 90% to 10% EDGE RATE - (trf) average of rise & fall

RISE PROPAGATION DELAY (tph. + put)

- max. time from input assigns 50% to output crossing 50% FALL PROPAGATION DELAY (tops, tops.)

- max. time from input assising 50% to output crossing 50%

PROPAGATION DELAY (tpd)

– average

CONTAMINATION DELAY

- fastest input 50% - output 50%.

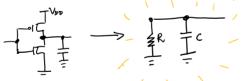

Recall First Order Circuits

PULL DOWN: Supple

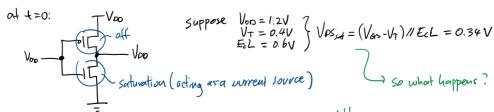

Suppose for 1=-60, imput is off, then PMOS pulls output up to 0, and assume at +=0, input switch to 1

We can model the Mos as resistor & capacitor:

tput is time to half. You

+ = R(. In(2)

## Effective Resistance Calculation

$$I_{DS} = C_L \cdot \frac{\Delta V}{\Delta t}$$

Voo=1.2V

So we're always in saturation!

Fil = 0.6V

So we're always in saturation!

$$\frac{1}{L} = C_{L} \cdot \frac{\Delta V}{\Delta t}$$

$$= C_{L} \cdot \frac{V_{DD} - V_{DD}}{t_{p}HL}$$

$$I_{DS} = C_{L} \cdot \frac{V_{DD}}{t_{p}HL}$$

$$I_{DS} = C_{L} \cdot \frac{V_{DD}}{t_{p}HL}$$

$$t_{pHL} = 0.7RC_{L} \text{ odso}$$

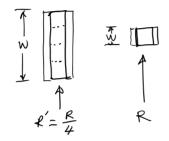

Note: (This) calculation is for unit transistor (W==L), If Wis larger, then resistance is smaller

Resistance of PMOS is typically (~2.5x) higher because undoiting of under (for PMOS) is much smaller.

The size of PMOS is bigger than NMOS is so that  $V_5$  is around the <u>middle</u> (recall  $W_N$  &  $W_P$  determines X)

from example:

Reg =

$$\frac{(Vdd/2)}{0.7 \times I_{sof}}$$

Reg =  $\frac{(Vdd/2)}{0.7 \times I_{sof}}$  Reg =  $\frac{(Vdd/2)}{0.7 \times I_{sof}}$  Reg =  $\frac{(Vdd/2)}{0.7 \times I_{sof}}$  L=W

Reg =  $\frac{(Vdd/2)}{0.7 \times I_{sof}}$  L=W

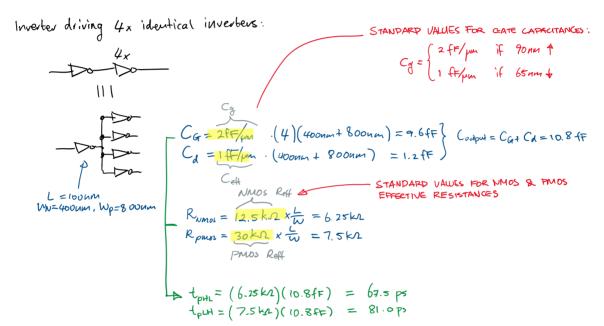

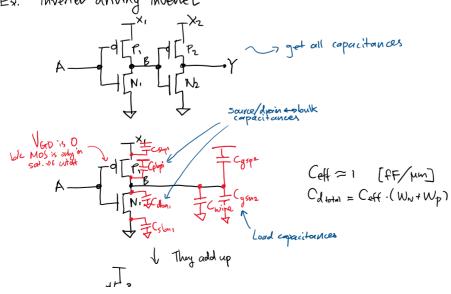

inverter driving inverter

Ex CMOS inventer has Pullup: 8 N: 2 N, 2N=L=200nm, N=100nm...

Pull Down: 42.2

Compute inverter delay using 0.18 nm tech. Assume roup input & Cwie = 0