## Design of CMOS inverter

( Noise-margin-centric approach)

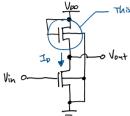

Recall components concerted to the Source is the DRIVER ground is the LOAD

Resistors are large & undesirable for implementation

## Saturation-Enhanced: Transistors driven by another transistor in saturation

- This is on if Vout >

$$V_{PD}+V_T$$

off if  $V_{OUT}< V_{PD}+V_T=7$  Vout is bounded on upper end

off if Vout

$$<$$

Vpp+V7 =7 Vout is bounded on upp

$V_{DH} = V_{DD} - V_{T}(V_{OH})$

function b/c top MOs Vs is not O

$V_{OH} = V_{DD} - \left(V_{TO} + \chi\left(\sqrt{V_{OH} + 2|\Phi_{F}|} - \sqrt{2|\Phi_{F}|}\right)\right)$

If we se using iterative process,

we can start with  $V_{OH} \approx V_{PD}$

If we're using Herative process, we can start with VOH > VPD

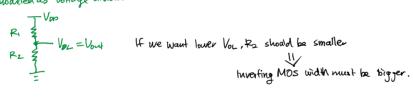

To find Von, equate the current

$$\begin{split} \mathbf{I}_{D_{\mathbf{I}}}\left(\text{lin}\right) &= \mathbf{I}_{DL}(\text{sat}) & \mathbf{I}_{\text{for inverting device}} \\ \mathbf{I}_{\text{op}} \text{ Mos always in Sat.} & \underbrace{V_{\text{os}}}_{\text{Up}} \cdot \frac{V_{\text{os}}}{\left(V_{\text{op}} - V_{\text{r_{I}}}\right)V_{\text{out}} - \frac{V_{\text{out}}^{2}}{2}\right)}_{\text{C}} = \underbrace{\frac{V_{L} \, V_{\text{sat}} \, C_{\text{out}} \, \left(V_{\text{op}} - V_{\text{out}} - V_{\text{r_{L}}}\right)^{2}}{\left(V_{\text{op}} - V_{\text{out}} + V_{\text{r_{L}}}\right) + E_{\text{cov}} \, L_{L}} \end{split}$$

Ratio of Width of two devices:  $K_R = \frac{W_I/L_I}{W_L/L_L}$

Countre modeled as voltage divider

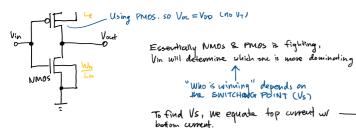

## Pseudo-NMOS Inverter

Vin only a PMOS like a NMOS — forcing gate to

$$V_{ob}$$

or GND

$$\frac{V_{DD}}{V_{DD}} = \frac{V_{DD}}{V_{DD}} = \frac$$

DISADVANTAGE: LOW -> HIGH propagation > a lot longar -> Because PMOS has lower mobility

- December 1 mus now rower magnity

Because hole mobility is lower than election trobility

and PMOS is small

So resistance is high

so time constant for pulling this large

so delay is longer

## CMOS Inverter

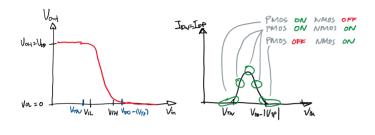

$$\frac{\left|W_{N}V_{\text{set}}\left(C_{\text{ox}}\left(V_{\text{b}}-V_{\text{m}}\right)^{2}\right|}{\left(V_{\text{s}}-V_{\text{m}}\right)+E_{\text{cx}}\cdot L_{N}}=\frac{\left|W_{\text{p}}V_{\text{set}}C_{\text{ox}}\cdot\left(V_{\text{bo}}-V_{\text{s}}-\left|V_{\text{tp}}\right|\right)^{2}}{\left(V_{\text{bo}}-V_{\text{s}}-\left|V_{\text{Th}}\right|\right)+E_{\text{cy}}\cdot L_{p}}$$

$$Assign X = \frac{\left|W_{N}E_{\text{cp}}L_{p}\right|}{\left|W_{\text{p}}E_{\text{cN}}L_{N}\right|}=\frac{\left|W_{N}E_{\text{cp}}\right|}{\left|W_{\text{p}}E_{\text{cN}}\right|}$$

$$But also X = \frac{\left|V_{\text{bo}}-V_{\text{s}}-\left|V_{\text{Th}}\right|\right|}{\left|V_{\text{s}}-V_{\text{T}}\right|} \qquad (ratio of "strength" of PMOS vs. NMOS)$$

$$V_{\text{s}} = \frac{\left|V_{\text{bo}}-V_{\text{s}}-\left|V_{\text{Th}}\right|\right|}{\left|V_{\text{s}}-V_{\text{Th}}\right|}$$

$\times$  If  $W_N > W_P$  ( $\uparrow X$ ), we shift the  $V_S$  left ( $\bullet$ )  $\star$  If  $W_P > W_N$  ( $\downarrow X$ ), we shift the  $V_S$  right ( $\bullet$ )

ELEC 402 Page 2